## CS/EE 217 GPU Architecture and Parallel Programming

### Lecture 6: DRAM Bandwidth

## Objective

- To understand DRAM bandwidth

- Cause of the DRAM bandwidth problem

- Programming techniques that address the problem: memory coalescing, corner turning,

## Global Memory (DRAM) Bandwidth

#### Ideal

#### Reality

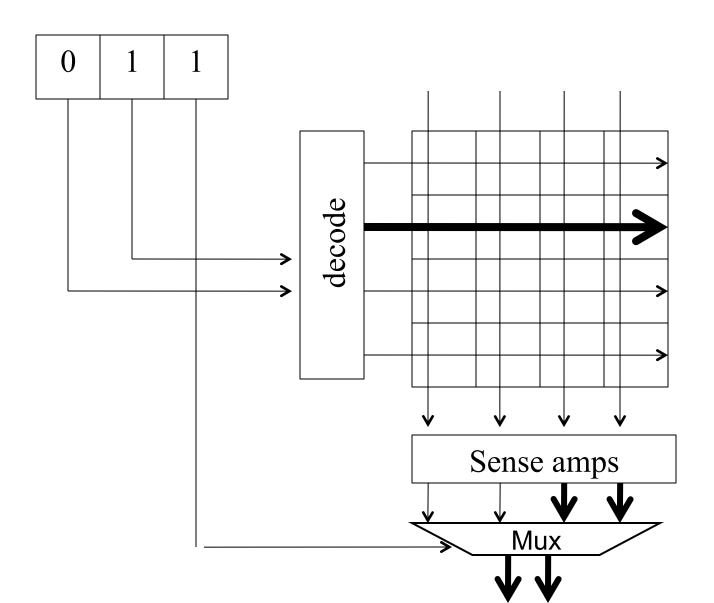

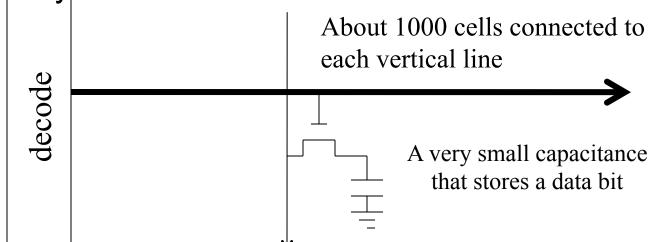

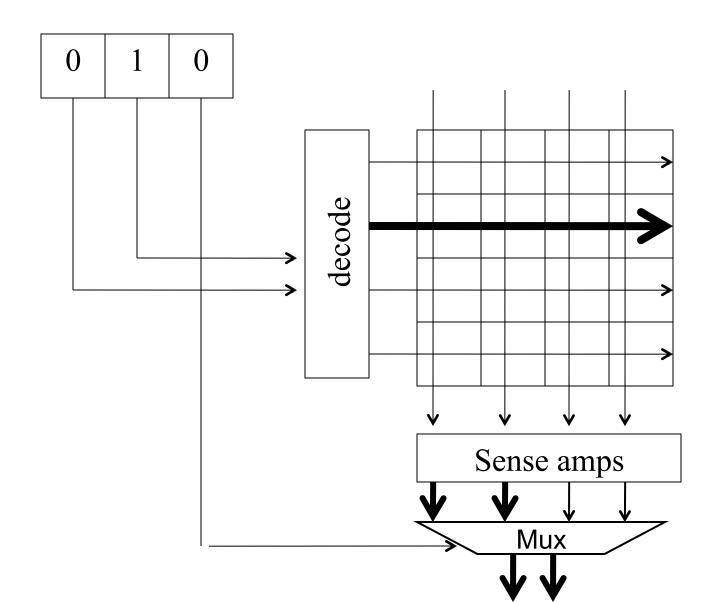

## **DRAM Bank Organization**

## A very small (8x2 bit) DRAM Bank

## DRAM core arrays are slow.

- Reading from a cell in the core array is a very slow process

- DDR: Core speed = ½ interface speed

- DDR2/GDDR3: Core speed = ¼ interface speed

- DDR3/GDDR4: Core speed = ½ interface speed

- likely to be worse in the future

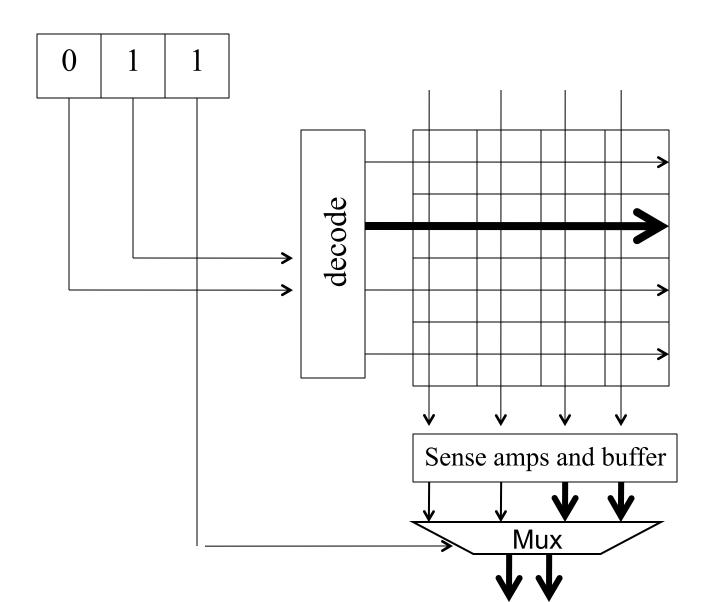

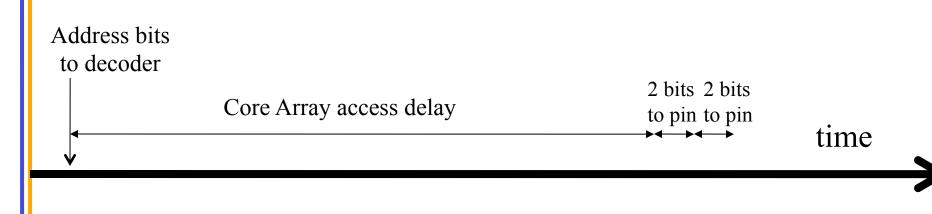

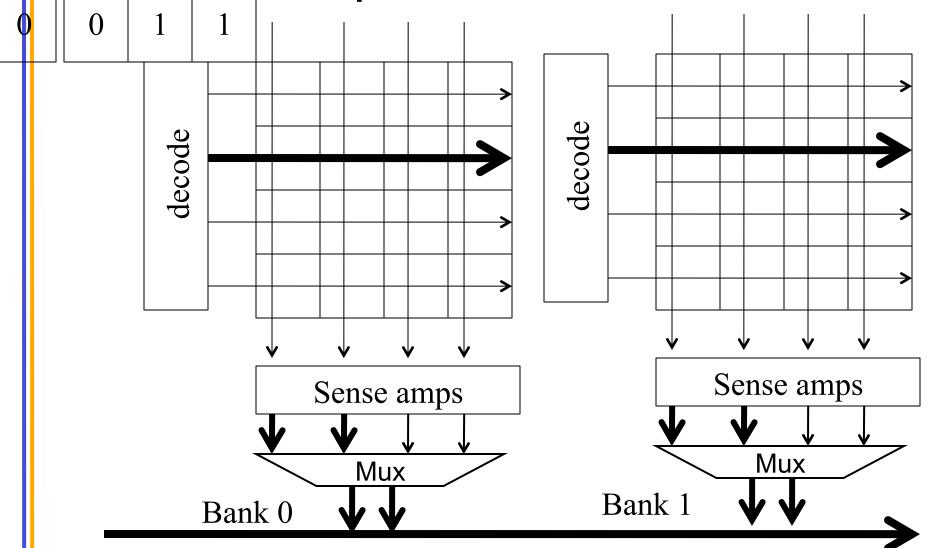

## DRAM Bursting.

- For DDR{2,3} SDRAM cores clocked at 1/N speed of the interface:

- Load (N × interface width) of DRAM bits from the same row at once to an internal buffer, then transfer in N steps at interface speed

DDR2/GDDR3: bufferwidth = 4X interface width

## **DRAM** Bursting

## **DRAM** Bursting

## DRAM Bursting for the 8x2 Bank

#### Non-burst timing

Modern DRAM systems are designed to be always accessed in burst mode. Burst bytes are transferred but discarded when accesses are not to sequential locations.

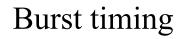

## Multiple DRAM Banks

## DRAM Bursting for the 8x2 Bank

# First-order Look at the GPU off-chip memory subsystem

- nVidia GTX280 GPU:

- Peak global memory bandwidth = 141.7GB/s

- Global memory (GDDR3) interface @ 1.1GHz

- (Core speed @ 276Mhz)

- For a typical 64-bit interface, we can sustain only about 17.6 GB/s (Recall DDR - 2 transfers per clock)

- We need a lot more bandwith (141.7 GB/s) thus 8 memory channels

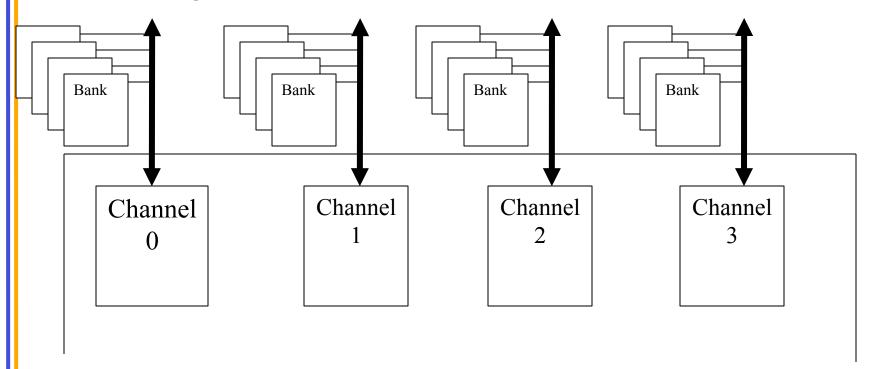

## Multiple Memory Channels

- Divide the memory address space into N parts

- N is number of memory channels

- Assign each portion to a channel

## Memory Controller Organization of a Many-Core Processor

- GTX280: 30 Stream Multiprocessors (SM) connected to 8-channel DRAM controllers through interconnect

- DRAM controllers are interleaved

- Within DRAM controllers (channels), DRAM banks are interleaved for incoming memory requests

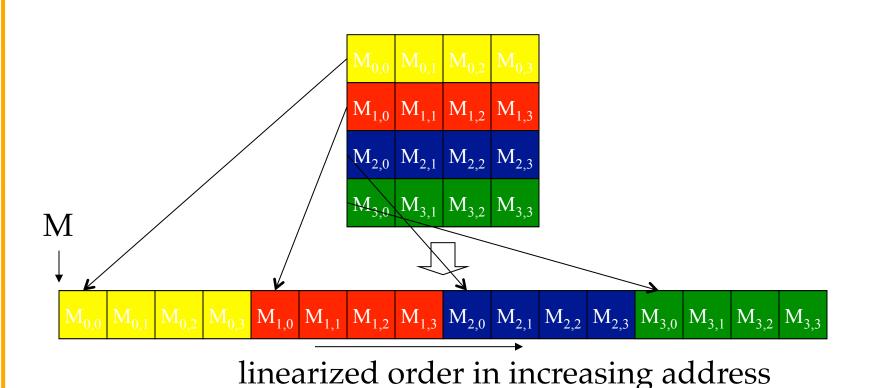

# Placing a 2D C array into linear memory space

## Base Matrix Multiplication Kernel

```

global__ void MatrixMulKernel(float* d_M, float* d_N, float* d_P, int Width)

// Calculate the row index of the Pd element and M \,

int Row = blockIdx.y*TILE WIDTH + threadIdx.y;

^{\prime}/ Calculate the column idenx of Pd and N

int Col = blockIdx.x*TILE WIDTH + threadIdx.x;

float Pvalue = 0;

// each thread computes one element of the block sub-matrix

for (int k = 0; k < Width; ++k)

Pvalue += d M[Row*Width+k]* d N[k*Width+Col];

d P[Row*Width+Col] = Pvalue;

```

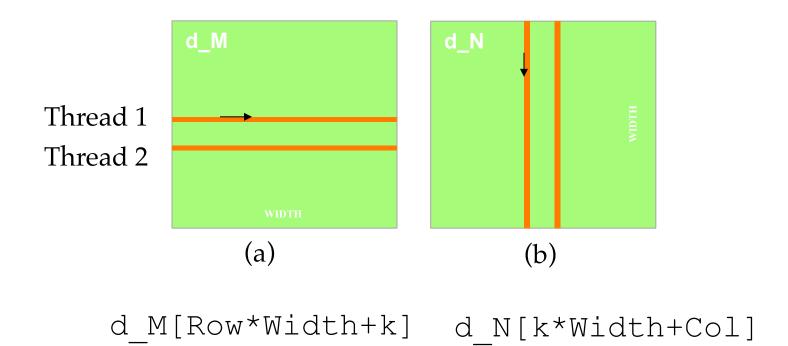

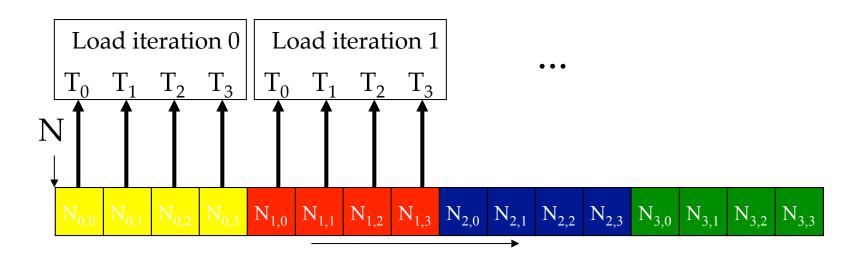

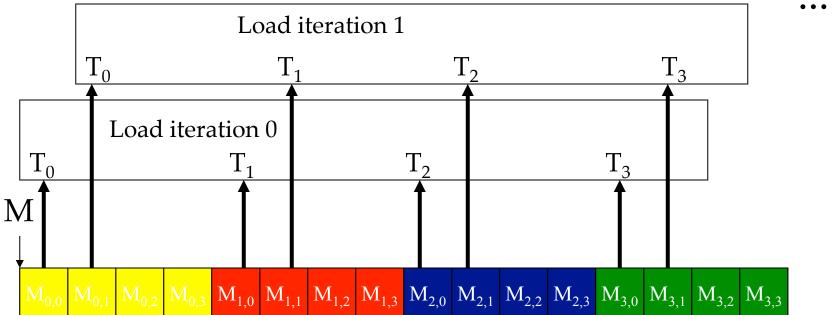

#### Two Access Patterns

k is loop counter in the inner product loop of the kernel code<sub>18</sub>

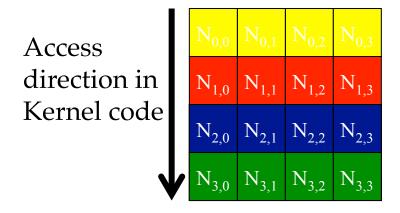

#### N accesses are coalesced.

#### M accesses are not coalesced.

Access direction in Kernel code

|           |                    |                  | $\Rightarrow$    |

|-----------|--------------------|------------------|------------------|

| $M_{0,0}$ | $M_{0,1}$          | $M_{0,2}$        | $M_{0,3}$        |

| $M_{1,0}$ | $\mathbf{M}_{1,1}$ | $M_{1,2}$        | M <sub>1,3</sub> |

| $M_{2,0}$ | $M_{2,1}$          | M <sub>2,2</sub> | $M_{2,3}$        |

| $M_{3,0}$ | $M_{3,1}$          | $M_{3,2}$        | $M_{3,3}$        |

d\_M[Row\*Width+k]

```

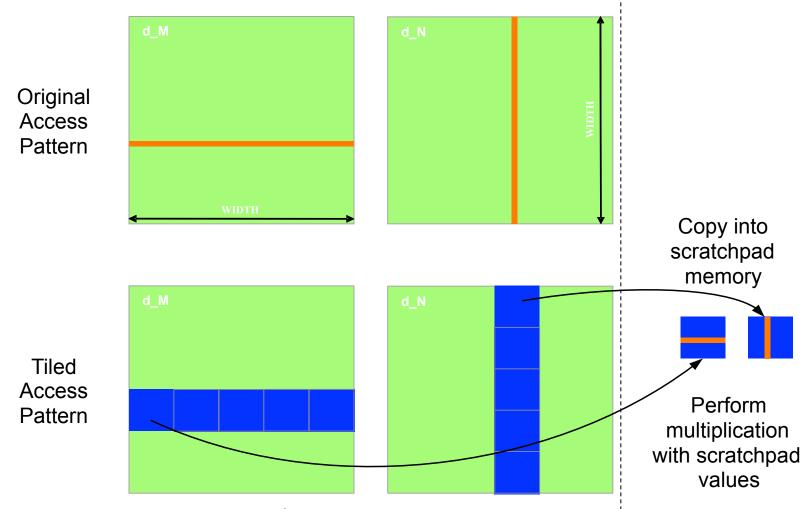

_global___ void MatrixMulKernel(float* d_M, float* d_N, float* d_P, int Width)

shared float Mds[TILE WIDTH][TILE WIDTH];

shared float Nds[TILE WIDTH][TILE WIDTH];

int bx = blockIdx.x; int by = blockIdx.y;

int tx = threadIdx.x; int ty = threadIdx.y;

Identify the row and column of the d P element to work on

int Row = by * TILE WIDTH + ty;

int Col = bx * TILE WIDTH + tx;

float Pvalue = 0;

Loop over the d M and d N tiles required to compute the d P element

for (int m = 0; m < Width/TILE WIDTH; ++m) {

Coolaborative loading of d M and d N tiles into shared memory

Mds[tx][ty] = d M[Row*Width + m*TILE WIDTH+tx];

10.

Nds[tx][ty] = d N[(m*TILE WIDTH+ty)*Width + Col];

__syncthreads();

12. for (int k = 0; k < TILE WIDTH; ++k)

Pvalue += Mds[tx][k] * Nds[k][ty];

__synchthreads();

d P[Row*Width+Col] = Pvalue;

```

Figure 6.10: Using shared memory to enable coalescing

## ANY MORE QUESTIONS? READ CHAPTER 6